GPU 顯存一般採用 GDDR 或 HBM 兩種方案, 傳統的 GDDR 主要通過提升 GDDR 的帶寬實現性能的提升. HBM 則將原本在 PCB 板上的 DDR 顆粒和 GPU 晶片同時集成到 SiP 封裝中, 使內存更加靠近 GPU, DDR Die 採用堆疊方式, 通過增加單個 DDR 容量和層數來實現內存容量和帶寬的提高.

HBM 優勢, 1) 節約晶片面積: 根據 AMD, 1GB HBM 相較 1GB GDDR5 能夠節省大約 94% 的晶片面積; 2) 在更低的頻率和更少的功耗下提供超越常規內存的帶寬: HBM 通過同一封裝內的矽中介層與 SoC 集成在一起, 能夠克服數據 I/O 封裝管腳限制的最大數量, 進而突破內存帶寬的限制.

HBM 已普遍搭配主流 AI 訓練晶片使用, 相較 GDDR 帶寬顯著提升. 如 Nvidia 的 DGX A100 單 GPU 搭載了總計 80GB容量的 HBM2E, DGX H100 單 GPU 搭載了總計 80GB容量的 HBM3, 單個 HBM3 存儲帶寬最高可達 819GB/s, 較單個 GDDR 帶寬提升 10 倍以上.

訓練型 AI 伺服器對於 HBM 市場的拉動體現在: 1) AI 伺服器滲透率的提升; 2) 單個 AI 伺服器搭載 GPU 數量的增加; 3) 每個 GPU 搭載的 HBM Stack 數量增加; 4) 單個 HBM 堆疊的 DRAM die 層數(Hi)增加, 以及 DRAM die 容量增加; 5) HBM 代際進步帶來單 GB 價值量的提升.

HBM 採用 2.5D+3D 封裝工藝, 包括 Bumping, RDL, FC, TSV, CoWoS 等. 封裝工藝主要有四項功能: 1) 保護晶片免受外部沖擊或損壞; 2) 將外部電源傳輸至晶片, 保證晶片的正常運行; 3) 為晶片提供線路連接, 以便執行信號輸入和輸出操作; 4) 合理分配晶片產生的熱量, 確保其穩定運行.

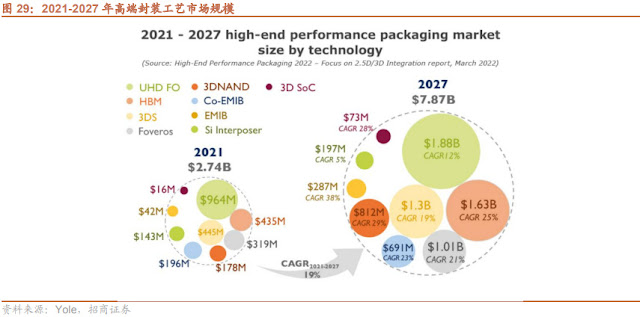

Yole 預計 2021 年針對 HBM 和 Si Interposer 的高端高性能封裝市場規模合計約 14 億美元, 其中 HBM 和矽中介層市場封裝規模分別為 4.35 億美元和 9.64 億美元. 預計 2027 年增至約 35 億美元. 矽中介層通常由台積電, 三星和聯電提供, 還包括 Intel 的 Foveros 方案.

HBM 工藝流程包括晶圓測試, 中段制造, 後段封測等環節, 一方面帶動部分傳統封裝工藝環節的設備價值量提升或帶來傳統封裝工藝變革, 另一方面, HBM 引入凸塊, RDL, TSV 等先進封裝工藝, 使得越來越多的檢/量測, 電鍍等前道設備融入中後段工藝中.

用來提高晶圓強度的襯底材料 90%以上均需要被去除, 背面減薄工藝可將晶圓減薄至 250um-20um. 2022 年全球晶圓減薄市場約 8.2 億美元, 主要為 DISCO, 東京精密等海外廠商壟斷. 先進封裝, Chiplet 等技術需要厚度更低的超薄晶圓, 將大幅提升對減薄設備的需求.

TSV 為 HBM 核心工藝, 成本占比接近 30%. 我們對 4 層存儲晶片和一層邏輯裸晶進行 3D 堆疊的成本進行分析, 考慮了 99.5%和 99%兩種鍵合良率的情形, TSV 形成和顯露的成本占比合計分別為 30%和 28%, 超過了前/後道工藝的成本占比, 是 HBM 的 3D 封裝中成本占比最高的部分.

TSV 通孔填充對性能至關重要, 銅為主流填充材料. TSV 加工流程包括孔成型, 沈積絕緣層, 減薄, 電鍍, CMP 等. TSV 成本結構中通孔填充占比 25%, 先進封裝驅動電鍍市場持續增長. TSV 工藝中, 通孔蝕刻占比最高為 44%, 其次為通孔填充和減薄, 分別為 25% 和 24%.

減薄拋光是 TSV 工藝中介於電鍍和鍵合之間的重要工序, 幫助實現 HBM 多層 DRAM die 堆疊. 晶圓廠一般負責 TSV 的成型工藝, 主要包括刻蝕和沈積, 封裝廠一般負責中段制程 (MEOL), 即矽通孔露出和背面金屬化工藝, 主要包括減薄, 鈍化和鍵合等. 在 HBM結構中, 減薄和鍵合工藝配合使用, DRAM die 之間不再需要導電凸塊, 晶片的厚度將薄數倍, 整體堆疊高度得以降低.

相較於 BT 基板, ABF 材質可用於線路較細, 高訊息傳輸的 IC, 比如 CPU, GPU 等晶片. ABF 作為基板的優勢在於, 銅箔基板上面附著 ABF 增厚薄膜就可以直接電鍍銅來形成金屬布線, 不需要熱壓過程. 在 HBM 中, 矽中介層一般採用 FC-BGA (球柵陣列封裝) 和下方封裝基板相連.

HBM 的 DRAM Die 由記憶體原廠負責生產和堆疊, 目前份額集中於三大原廠 SK 海力士, 三星, 美光, 根據集邦咨詢, 2022 年三大原廠 HBM 市占率分別為 SK 海力士 50%, 三星約 40%, 美光約 10%, 其中 SK 海力士是 HBM3 產品的領先生產商, 是 Nvidia AI 伺服器 GPU 的主要供應商.

HBM 產業鏈主要由 IP, 上游材料, 晶粒設計制造, 晶片制造, 封裝與測試等五大環節組成. DRAM 晶粒供應鏈主要廠商為三星, 海力士與美光, 晶片制造與封裝廠商主要為擁有 CoWoS 技術的台積電, I-Cube 技術的三星, EMIB 技術的 Intel 等擁有 2.5D/3D 封裝技術的 Foundry/IDM 廠商, 測試領域則由傳統封裝測試廠商如日月光, Amkor 等占據.

回覆刪除HBM 門檻高,SK 海力士「贏者全拿」Q3 DRAM 市占創高

https://technews.tw/2023/11/24/sk-hynix-hbm-dram/

生成式AI需求點火 HBM、DDR5明年聲勢旺

回覆刪除https://www.ctee.com.tw/news/20231118700113-439901

AI 晶圓營收明年達 30 億美元、HBM 消耗 6 億 GB!大摩點名供應鏈

回覆刪除https://finance.technews.tw/2023/11/07/high-bandwidth-memory/

AI芯片市场对HBM的需求持续上升

回覆刪除https://xueqiu.com/2758492053/265368246

台積電擴充CoWoS產能 設備廠樂看明年成長

回覆刪除https://ec.ltn.com.tw/article/paper/1616977

輝達 AI 先進封裝需求熱,法人:台積電改機增 CoWoS 產能

回覆刪除https://finance.technews.tw/2023/11/06/tsmc-cowos/

5大客戶狂追單!台積電CoWoS明年增產20%

回覆刪除https://www.ctee.com.tw/news/20231113701052-430501

穎崴明年營運樂觀 CoWoS封裝測試探針卡漸放量

回覆刪除https://www.cna.com.tw/news/afe/202311230136.aspx

台積電CoWoS封裝擁優勢 力成:1年內沒廠商可替代

回覆刪除https://www.ftvnews.com.tw/news/detail/2023A25W0030

萬潤打入台積CoWoS鏈

回覆刪除https://www.sinotrade.com.tw/richclub/news/655b8282271c1d5945c82b62

先進IC封裝技術往TSV 3D IC為必然發展方向

回覆刪除https://www.digitimes.com.tw/tech/dt/n/shwnws.asp?id=0000592916_922LRTQH0M8MGZ7LGGQAU

聯電TSV量產 獲超微晶片訂單

回覆刪除https://www.chinatimes.com/newspapers/20150721000142-260204?chdtv

〈昇陽半展望〉先進製程加持 今年營收逐季揚、全年創新高

回覆刪除https://news.cnyes.com/news/id/5264338

世界先進評估跨入晶圓薄化

回覆刪除https://www.chinatimes.com/realtimenews/20191231002404-260410?chdtv

AI 晶片 CoWoS 封裝產能受限,中介層不足成關鍵

回覆刪除https://technews.tw/2023/08/26/ai-chip-cowos/

輝達非台積CoWoS鏈 聯電搶頭香 擴產2倍

回覆刪除https://www.ctee.com.tw/news/20230825700567-430502