開發先進制程成本高企, 投入產出比低. 以台積電為例, 其提升至 7nm 節點時, 晶體管數量提高到 1.84 倍, 在相同的速度下功耗降低 30%. 而 5 nm工藝在相同的功耗下, 速度卻只能提高 15%! 同時半導體制造代工廠隨著制程的提升數量越來越少, 超越摩爾定律, 先進封裝大有可為.

More than Moore 採用先進的封裝技術將處理, 類比/射頻, 光電, 電源, 傳感等使用高速接口集成在系統內, 進行系統級封裝以實現系統性能的提升. 在晶片前道工藝技術節點受限的情況下, 先進封裝技術通過優化晶片間互連, 在系統層面實現算力, 功耗和集成度等方面的提升, 是突破摩爾定律的關鍵技術方向.

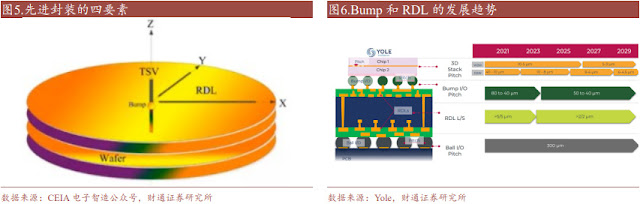

Bump, RDL, TSV, Wafer 為先進封裝的四要素, 具備任意一個均可以被稱為先進封裝. Bump 能夠互聯界面和緩沖應力, RDL 使 XY 平面的電氣延伸, TSV 讓 Z 軸的電氣延伸, Wafer 則作為集成電路的載體以及 RDL 和 TSV 的介質和載體不斷擴大.

凸點 (Bump): 先進封裝演化的基礎. 凸點是指定向生長於晶片表面, 與晶片直接或間接相連接的具有導電特性的凸起物. 在先進封裝中, 有源面上有凸點電極的晶片向下放置, 直接與封裝基板/基板布線層進行鍵合, 而凸點代替傳統封裝中的引線, 起到電互連, 熱傳遞和機械支撐的作用.

凸點間距逐漸減小, 凸點密度增大帶動帶寬和功耗雙提升.隨著電子器件向更輕薄, 微型和高性能進步, 凸點間距向 20μm 推進, 巨頭已經實現小於 10μm 的凸點間距. 在 20μm 時, 內部互聯使用 TCB 技術, 10μm 以下時, 混合鍵合 (Hybrid Bonding) 技術可以實現更小凸點間距和更高凸點密度.

RDL (Re-distributed layer) 在晶圓表面沈積形成金屬層和相應的介質層, 並形成金屬布線. RDL 的優勢主要有三點: 1)能代替部分晶片內部線路的設計, 降低設計成本; 2) 支持更多的引腳數量; 3)可以使 I/O 觸點間距更靈活, 凸點面積更大, 從而使基板與元件之間的應力更小, 元件可靠性更高.

根據 RDL 分布的凸點位置不同, 晶圓級封裝 (WLP) 可分為扇入型 (FIWLP) 和扇出型(FOWLP) 兩種封裝類型. 1) 扇入型需要將所有的 I/O 端口都放置在晶片尺寸範圍內, 通常用於低 I/O 數量和較小裸片尺寸的工藝. 2) 扇出型將 I/O 端口放在晶片尺寸範圍外, 突破 I/O 引出端數目的限制.

TSV (Through Silicon Via) 在晶片和晶片之間, 晶圓和晶圓之間制作垂直導通孔並填充金屬等導電材料來實現晶片垂直互連, 是 2.5D/3D 封裝的關鍵工藝. TSV 技術將晶片上下層的互聯路徑, 或者晶片正面與背面的路徑長度縮短, 使平面型的晶片結構拓展到垂直型的疊層結構.

TSV 制造和多片晶圓堆疊鍵合需要將晶圓減薄. 晶圓減薄不會影響其電學性能, 但會顯著降低其機械性能. 隨著先進封裝與 3D 集成的發展, 部分晶圓需要減薄至 30μm 甚至 10μ m 以下, 如今 TBDB 技術已經成為面向大尺寸超薄晶圓的拿持與後道工藝加工處理的重要解決方案.

Chiplet (小晶片) 具有較強的異質異構集成特征. Chiplet 將一塊功能完善且集成度很高的裸片拆分成多種具有單一特定功能並可單獨設計, 測試和生產的小晶片, 再通過先進封裝技術集成為系統級晶片組.

由於是將不同功能, 不同工藝制造的晶粒封裝成一個 SoC 晶片, Chiplet 技術相 比 SiP 在成本, 規模, 周期均有優勢. 另外, 因為使用 2.5D, 3D 等先進封裝技術實現晶片上互聯, Chiplet 的集成度更高, 功耗更低, 延遲更低, 工作頻率更高.

根據 Yole 數據, 受 5G, AI, HPC 等因素影響, 2022 年全球封裝市場規模約為 950 億美元, 其中先進封裝市場規模為 443 億美元, 占比 47%; 預計到 2028 年, 全球封裝市場規模將達到 1433 億美元, 其中先進封裝市場規模 786 億美元, 占比 55%, 相應 CAGR 為 10.03%.

英特爾, 台積電, 三星憑借其晶圓廠在前道環節的優勢, 主導了先進封裝領域的技術路線和訂單分配, OSAT 工廠只能分擔此類廠商的產能壓力或供應先進封裝的低端環節. 因此, 除技術外, OSAT 廠商需要與上游廠商密切合作以獲取先進封裝訂單.

從技術布局來看: 先進封裝集成技術主要包括 2D, 2.5D, 3D, 3D+2D, 3D+2.5D 多種類型. 由於先進封裝中的部分高難度工藝涉及到晶圓制造技術, 疊加高端晶片對制造和封測配合緊密度需求的加深, 因此晶圓代工廠相較封測廠具備天然的優勢.

台積電先進製程/封裝擴產持續,全台北中南大規模建廠

回覆刪除https://finance.technews.tw/2024/03/07/tsmc-expands-factories-across-taiwan/

CoWoS先進封裝需求大增,WoS FT今年訂單可望倍增,京元電子進補

回覆刪除http://www.investor.com.tw/onlinenews/NewsContent.asp?articleNo=14202403060093

東吳證券:先進封裝賦能高速計算 算力需求提升

回覆刪除https://hk.investing.com/news/stock-market-news/article-473707

SK海力士砸10億美元發展先進封裝 鞏固HBM晶片領導地位

回覆刪除https://www.worldjournal.com/wj/story/121209/7815781

先進封裝需求看好 日月光、京元電爆量漲停作收

回覆刪除https://ec.ltn.com.tw/article/breakingnews/4600193

AI浪潮,帶動記憶體晶片再進化

回覆刪除https://hao.cnyes.com/post/72690?utm_source=cnyes&utm_medium=home&utm_campaign=postid