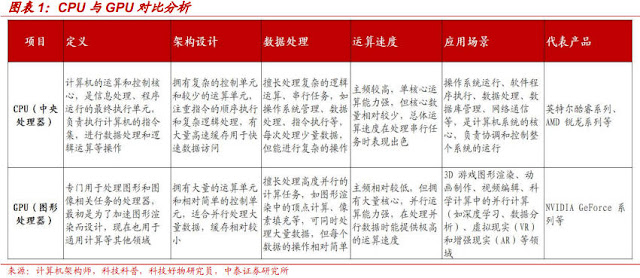

CPU 和 GPU 均為運算核心晶片產品, 但其在架構設計, 數據處理, 運算速度以及應用場景上有所區分. CPU 是計算機系統的運算和控制核心, 即信息處理, 程序運行的最終單元. GPU 最初是為了加速計算機圖形渲染而設計的專用處理器. 但隨著技術的發展, GPU 的應用範圍已經遠遠超過了傳統的圖形處理, 成為通用計算的重要組成部分.

FPGA 是在 PAL (可編程陣列邏輯), GAL (通用陣列邏輯) 等可編程器件的基礎上發展起來的產物, 屬於一種半定制電路, 是可重構的晶片, 可根據用戶的需要, 在制造後進行無限次數的重覆編程, 以實現想要的數位邏輯功能. FPGA 包括三種可編程電路, 可編程邏輯塊 (CLB), 輸入/輸出模塊 ( IOB) 及可編程互聯資源 (PIR).

ASIC 晶片面向專項任務, 其計算能力和計算效率均嚴格匹配於任務算法, 較為適用於各行各業的推理場景. ASIC 是指專用集成電路 (ApplicationSpecific Integrated Circuit), 是一種專用於特定任務的晶片. 官方定義為: 應特定用戶要求, 或特定電子系統的需要, 專門設計, 制造的集成電路. ASIC 還可進一步細分有 TPU, NPU, DPU 及其他.

CPU, GPU, FPGA, ASIC 靈活性依次為從高到低, 但是能效上依次為從低到高. CPU 和 GPU 是遵循馮.諾依曼體系架構, FPGA 和 ASIC 是哈佛架構. 運算單元上, GPU 比 CPU高, FPGA 因為幾乎沒有控制模塊, 比 GPU 更高. 功耗上, GPU的功耗極高. 未來隨著 ASIC 加速崛起, 有望提升市場占比. 同時, 結合 CPU, GPU, FPGA 等多種晶片的異構計算加速普及.

精度範圍: ASIC 專注低精度計算, 與大模型訓練需求匹配; GPGPU 則更靈活, 支援多精度場景.算力性能: GPGPU 在低精度算力上領先, 如輝達 GB200 表現突出, ASIC 相對落後. 功耗與能效比: ASIC 因定制化設計通常更節能 (如 Maia 100), 但 GPGPU 在某些案例 (如 A100) 也能展現高效性, 視具體架構而定.

顯存性能: GPGPU憑藉 HBM 技術在帶寬和容量上領先 ASIC, 而 LPU 以超高內存帶寬突破瓶頸. 算力密度: ASIC 在特定任務中展現高算力密度, GPGPU 則受限於通用性, LPU 未明確數據但具潛力. 算術強度: ASIC 技術進步顯著, LPU 則以存力優勢支持低算術強度任務. 特殊優勢: ASIC 擅長特定任務優化, GPGPU 適應多場景, LPU 通過高帶寬設計為大模型推理提供數據保障.

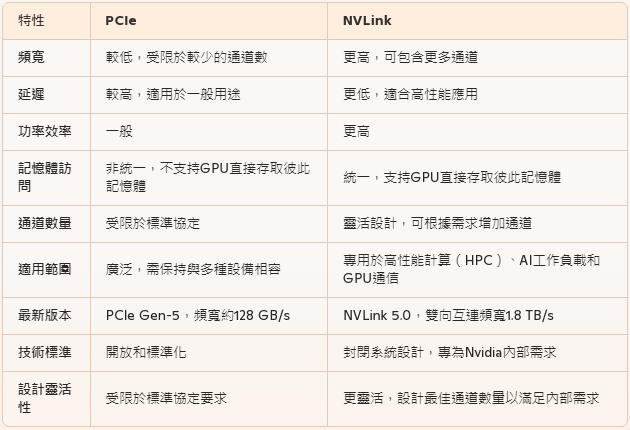

互連: NVLink 主導下的技術挑戰與突破. 輝達 NVLink 所能實現的 Scale-up 互連能力一騎絕塵. GB200 所依賴的 NVLink 5.0 技術能夠實現 1.8TB/s 的互連速度, 而其他廠商的 Scale-up 互連大多以 PCIe 協議為基礎, 目前 PCIe5.0 技術單通道雙向速率為 8GB/s, 16 通道可達 128GB/s, 遠遠低於 NVLink 同代技術. 從技術節奏來看, 挑戰輝達 NVLink 的難度較大.

為什麽大廠紛紛開始自研 AI 晶片? 從自研成本測算說起通常來說一個晶片公司的支出有以下四個方面: 員工薪資, EDA 和 IP 費用, 晶片制造費用, 銷售費用. 以谷歌 TPU 與博通外包服務模式為例, 這其中有部分由博通承擔, 但最終谷歌都需要支付相應的價格. 對於一家數位晶片Fabless 公司而言, 員工薪資約占總支出 60%, 占掉大部分的比重.

1) 訓練端: 從訓練集群的規模上看, 各廠商陸續建成萬卡集群, 其中比較有代表性的是 Meta 於 24/03 月宣布的兩個 24k GPU 集群 (共 49152 個 H100). 24H2 以來市場最為關注的是 xAI 建設的 10 萬卡 H100 集群. 2) 推理端: 輝達數據中心有 40% 的收入來自推理業務. 隨著 AI 應用遍地開花, 我們認為 AI 推理需求還有更大滲透空間.

博通產品線 IP 生態強大完善, 在接口, 互連等領域保持前瞻性優勢. 接口方面, 博通針對不同規模的 AI 集群提供差異化系統架構與解決方案. 一類是 Endpoint Scheduled 系統架構, 其主要面向的是小規模 AI 集群數據調度, 各計算節點 (如 GPU) 之間通過 Tomahawk 5 以太網交換晶片來進行互聯. 另一類是對於大規模 AI 集群, 需要由智能交換器負責數據調度的 Switch Scheduled 架構中.

Marvell 通過 HBM 重構與 CPO 集成的雙重突破體現競爭力, 直擊 AI 晶片的能效與帶寬瓶頸. 通過非行業標準的 HBM I/O 接口設計, 實現接口功耗降低 70%, 將 HBM 支持電路從 XPU (AI 加速器) 邊緣移至堆疊底部的基礎裸片, 釋放 XPU 晶片 25%的面積用於計算單元擴展. 優化後, 單一 XPU 可連接的 HBM 堆棧數量提升至高 33%, 降低了雲運營商的 TCO.

世芯通過垂直堆疊與納米片晶體管技術直擊 AI 與高性能計算晶片的能效與算力瓶頸. 世芯已正式開放其面向 AI 和高性能計算應用的最新高性能 ASIC 的三維集成電路 (3DIC) 設計服務, 通過矽通孔 (TSV) 和混合鍵合技術實現多晶片垂直堆疊. 世芯經過矽驗證的 3DIC 設計流程從三個關鍵維度優化了選定的 3DIC 設計: 功率傳輸, 晶粒間電氣互連和系統範圍的熱特性.

創意的技術競爭力體現在先進制程覆蓋與系統級設計能力兩大維度. 創意提供的 SoC 設計服務涵蓋了 0.5um 到先進的 5nm/4nm/3nm 等工藝節點制程, 包括各種產品形態的晶片設計實現. GHz 工作頻率, 深亞微米噪聲耦合, IR 壓降, 靜電 (ESD) 放電, 可制造性設計 (DFM), 良率設計提升 (DFY) 與嚴峻上市時程需求的挑戰.

AI ASIC 優勢在於針對特定任務 (如大模型推理) 優化, 效率高, 成本低, 功耗少, 適合數據中心, 且硬件控制提升安全性. 劣勢包括高初始成本, 缺乏靈活性, 開發周期長及技術過時風險. 總體看, ASIC 在性能與能效上具潛力, 但需權衡投資與適應性, 適用於專用場景, 與靈活但能效低的 GPGPU 形成對比, 企業需依需求謹慎選擇.

ASIC獨熱,反映IC設計業市況清淡?

回覆刪除https://www.moneydj.com/kmdj/news/newsviewer.aspx?a=e29dff17-ba1f-4cac-9547-4e1aa464a177

聯發科於MWC 首次展示ASIC晶片

回覆刪除https://money.udn.com/money/story/5612/8583871

奇鋐去年EPS首破20元;ASIC晶片動能靚

回覆刪除https://www.moneydj.com/kmdj/news/newsviewer.aspx?a=f0482fd6-0cd7-4238-8368-04ac12142f9e

里昂:未來數年 ASIC 產業持續樂觀 按讚世芯、創意

回覆刪除https://money.udn.com/money/story/5710/8573885

DeepSeek是正面消息、ASIC將與GPU共存 外資仍看好Nvidia

回覆刪除https://money.udn.com/money/story/5599/8563630

CSP採雙供應商策略 ASIC業迎新局

回覆刪除https://www.chinatimes.com/newspapers/20250315000313-260206?chdtv

摩根士丹利:美國AI半導體-市場對於ASIC的熱情開始顯得過度了

回覆刪除https://hao.cnyes.com/post/136272