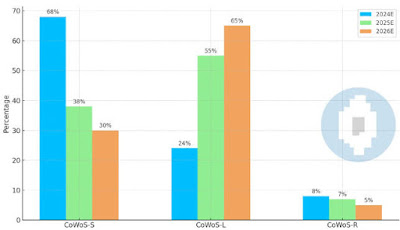

2025 年全球對 CoWoS 及類似封裝產能的需求或將增長 113%. 主要供應商台積電, 日月光和安靠正在擴大產能. 到 2025 年第四季度末, 台積電的月產能預計將增至 6.5 萬片以上 12 英寸晶圓當量, 而安靠和日月光合用產能將增至 1.7 萬片晶圓. 受惠於輝達 Blackwell 系列 GPU 量產, 台積電將從 2025 年第四季開始由 CoWoS-S 轉為 CoWoS-L 制程.

根據半導體創芯網數據 CoWoS 工藝將漲價 15%到 20% (供不應求), 這一調整既源於 AI 領域對計算能力的需求激增, 也顯示了制程技術成本的不斷上升. 除了最大的客戶輝達系列產品採用 CoWoS 技術外, AMD 的 MI300 採用台積電 SoIC (3D) 和 CoWoS (2.5D) 兩種封裝技術. 博通, Marvell, 微軟, 亞馬遜, 谷歌對於 CoWoS 也存有一定需求.

CoWoS-L 確保良好的系統性能同時避免大型矽中介層良率損失. CoWoS-L 中介層包括多個本地矽互連 (LSI) 晶片和全域再分布層 (RDL), 形成一個重組中介層 (RI), 以取代 CoWoS-S 中的單片矽中介層. LSI Chiplet 與 CoWoS-S 相比保留了亞微米級銅互連, 矽通孔 (TSV) 和嵌入式深溝電容器 (eDTC), 以確保良好系統性能, 同時避免大型矽中介層良率損失問題.

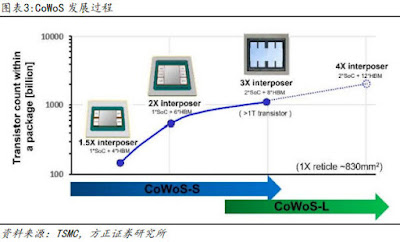

CoWoS-L 無需光罩拼接, 解決大型矽中介層良率問題, 帶來更高靈活性. 目前, 台積電已成功實現具有 3 倍光罩版尺寸的中介層的 CoWoS-L 結構, 搭載多個 SoC/晶片和 8 個 HBM, 穩定的可靠性結果和卓越的電氣性能表明, CoWoS-L 架構有望延續 CoWoS-S 的勢頭, 滿足未來 2.5D SiP 系統在 HPC 和 AI 深度學習中的需求.

CoWoS-S 封裝因其矽中介層尺寸較小而面臨限制, 這種限制阻礙了其支援先進半導體應用 (如 Chiplet 設計) 所需的晶片數量不斷增加和面積更大的能力. CoWoS-L 專為滿足這些需求而設計, 提供 4~10 個光罩版的更大基板尺寸, 這允許在基板上實現更多晶片, 使 CoWoS-L 成為下一代高密度封裝解決方案的理想選擇, 符合更大面積和增加晶片整合度的趨勢.

CoWos-S 的關鍵問題是矽很脆, 隨著中介層變大, 處理非常薄的矽中介層會變得更加困難, 這些大型矽中介層的成本也變得越來越高. 有機中介層可以解決這個問題, 它們不像矽那麼脆, 但它們缺乏矽的電氣性能, 因此無法為更強大的加速器提供足夠的 I/O, 可以使用矽橋來補充訊號密度以進行補償, 這些橋比大型矽中介層具有更高的性能/複雜性.

Nvidia GB200 是 Blackwell 系列的關鍵組件, 將採用 CoWoS-L 技術, 由於基於 RDL 的中介層/LSI製造良率較低, CoWoS-L 良率仍較低且不穩定 (摩根大通認為目前只有 60% 左右, 遠低於 CoWoS-S 的 90%+ 水準). CoWoS-L 製程具有用於基板級散熱的石墨薄膜,但一些材料變形挑戰也會導致一些良率損失.

CoWoS-L 封裝包括: 頂層晶片通過 micro bump 並排粘接在中介層上. 中介層在將所有頂層晶片組成晶片-晶圓 (CoW) 中扮演重要角色, 而 LSI 則負責大部分晶片間的通信. 中介層的上面和下面分別都有 RDL 層, 分別對應微凸點和 C4 凸點. 由環氧塑封料包圍的 TIV 提供了從基板到頂層晶片的直接垂直路徑, 具有低插入損失的優點. 最後, CoW 晶片粘接到基板上並完成組裝.

CoWoS-L 結合了 InFO 和 CoWoS 的優勢, 將矽橋, 被動器件和 RDL 等集成, 從而優化良率, 控制翹曲, 提升系統性能等的一種封裝形式. 相比 CoWoS-S 中介層一整片晶圓的應用, OSAT 廠商對於 CoWoS-L 的 TIV 以及 organic interposer 上下表面的 RDL 技術都比較成熟, OSAT 廠商在 CoWoS-L 結構中的角色有望比在 CoWoS-S 中更重要.

相比矽中介層, CoWoS-L 的有機中介層與 top die 的 CTE 區別更大. 熱壓鍵合通過 Bond Head 和 Bond Stage 的結構完成待鍵合晶片之間的高精度對準, 並可在鍵合過程中施加一定的壓力以輔助鍵合. 熱壓鍵合在高精度鍵合領域表現更為出色, 使用 TCB 可以封裝更薄的晶片, 也可以使 I/O 間距更小.

在台積電 InFO 封裝中, 需要構建 TIV (Through InFO Via) 大銅柱實現上下兩個 package 的連接. 在 CoWoS-L 的有機中介層中同樣有一個 TIV (through insulator via) 結構, 根據 Lam, 大銅柱通常其高度和寬度是標準銅柱的五倍左右, 構建大銅柱的傳統方法是常規電鍍, 耗時較長, 且通常不均勻, 電鍍大銅柱的高度將隨著局部電流載荷密度的不同而變化.

CoWoS 製程涉及臨時鍵合機和解鍵合機, 這對於中介層上 TSV 的形成至關重要. 台積電的 RDL 中介層臨時鍵合機由德國 Suss Microtec 提供, 矽中介層臨時鍵合機由日本 AIMechatec 獨家提供, CoWoS 解鍵合機由日本 Tazmo 提供. 傳輝達最近削減了10萬片 CoWoS-S 晶圓產能 (台積電 6萬片+OSATs 4萬片), 最大的輸家將是 AImechatec.

台積電的 CoWoS-S 矽中介層又大又薄, 有破裂的風險, 而 CoWoS-R/L 中使用的 RDL 中介層則不存在這個問題. 然而, 由有機材料製成的大尺寸 RDL 中介層也面臨不同的問題 "翹曲". 為了解決這個問題, 歐洲的 SUSS MicroTec 專門為 TSMC 開發了一種具有壓力退火功能的臨時鍵合工具, 有助於緩解大型 RDL 中介層的翹曲問題.

台積群創廠傳交接 拚產CoWoS-L

回覆刪除https://www.ctee.com.tw/news/20250114700071-439901

黃仁勳回應砍單傳言!需求轉換至CoWoS-L 對台積電訂單持續增加

回覆刪除https://www.nownews.com/news/6635819

郭明錤:輝達產線更新,符合台積電擬主推 CoWoS-L

回覆刪除https://technews.tw/2025/01/15/ming-chi-kuo-nvidia-tsmc-cowos-l/

CoWoS砍單是謠言! 設備股吞定心丸、今年續衝鋒

回覆刪除https://www.moneydj.com/kmdj/news/newsviewer.aspx?a=f1f27426-cc12-4a9d-a4dc-db5dd3e11857

黃仁勳力挺CoWoS!來台首站,為何直奔台中矽品?

回覆刪除https://www.cw.com.tw/article/5133744

英伟达大砍台积电先进封装CoWos订单?究竟发生了什么?

回覆刪除https://wallstreetcn.com/articles/3739170

Nvidia shifts to CoWoS-L packaging for Blackwell GPU production ramp-up

回覆刪除https://www.tomshardware.com/tech-industry/nvidia-shifts-to-cowos-l-packaging-for-blackwell-gpu-production-ramp-up

黃仁勳:CoWoS產能今年將大幅提升

回覆刪除https://www.epochtimes.com/b5/25/1/16/n14414955.htm

Nvidia reportedly prioritizing dual-die Blackwell GPUs with CoWoS-L packaging

回覆刪除https://www.tomshardware.com/pc-components/gpus/nvidia-reportedly-prioritizing-dual-die-blackwell-gpus-with-cowos-l-packaging

大摩把脈2025年CoWoS:需求仍然強勁 GB300A將承接MI325與TPU釋出的CoWoS-S產能

回覆刪除http://www.aastocks.com/tc/usq/quote/stock-news-content.aspx?symbol=TSM&id=ZT1237901

輝達減少CoWoS-S產能需求!郭明錤直指1關鍵 對台積電影響曝光

回覆刪除https://tw.nextapple.com/life/20250115/5E678C6A560F4F585B93F88D87D84AA7