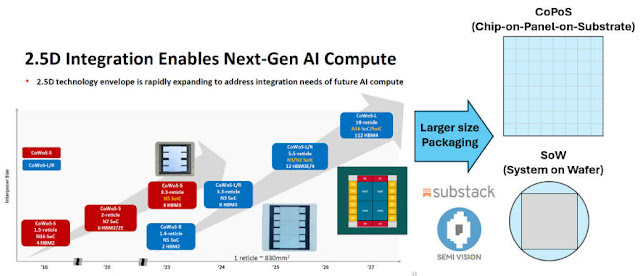

根據 Yole 發布的數據顯示, 在 AI, HPC 的推動下, 2023-2029年先進封裝市場的年複合增長率為 11%, 預計到 2029 年將達到 695 億美元. 其中, CoWoS 等 2.5D/ 3D先進 IC 封裝技術在 2023-2029 年間的年複合年增長率為 15%, 至 2029 年將占近 40%市場, 並成為代工廠, 封測廠, IDM, 晶片設計廠商以及 EDA 廠商都競相關注的一環.

然而 CoWoS 的全球產能非常緊張, CoWoS 封裝還面臨成本的挑戰, 台積電也在尋求降本的可能, 於是 CoWoS 衍生出了三大種類 (-S/-R/-L) 隨著晶片越做越大, 大晶片的良率不斷下降, 每片晶圓可切割出的晶片數量越來越少, 這一定程度上又逆向推動晶片價格不降反升. 面對以上行業挑戰, 業界一致認為 CoPoS 將更好地滿足下一代更高密度 AI 晶片.

AI 晶片未來可能會達到 80x84mm 的大型 die size 的趨勢, 12" 晶圓只能放下 4 片這樣的 die; 再加上良率問題, 單片晶片的成本會顯著提升. 如果將 "W" 換成 "P", 自然達成更高的面積利用率及顯著提升的產能. CoPoS 就是將中介層進行 "面板化", 做到所謂 Panel RDL; 或者說將 die 放到 "板級 RDL 層" 之上, CoPoS 可能是個更著眼於部分替代 CoWoS-R 和 CoWoS-L.

CoPoS 是 CoWoS 的面板化解決方案, 作為 2.5D 封裝的另外一種選擇, 未來先進的技術方向有望將矽中介層替換成玻璃中介層或板級封裝 RDL 層, BT 基板替換成玻璃基板, 相比 CoWoS 中的 FOWLP, 可以將多個晶片, 被動組件和互連集成在一個封裝內, 並以 RDL 工藝, 將晶片重新分布在具有面積利用率優勢的方形基板上進行互連, 更具產能優勢和成本效益.

下層, 也就是面板級封裝目前最廣泛的應用主要是 PMIC, RF IC, 線寬線距約在 10μm-5μm 左右. 中間則指向消費級 CPU, GPU, 在 5μm~2μm 線寬線距級別的產品已經在 "小批量生產". 上層則是面向 HPC, AI 等高端晶片, 這類晶片的面積更大, 晶圓級封裝的短板更明確得暴露; 面板級封裝在成本和效率方面的優勢會體現得更明確, 線寬線距要求更高, 可能需要 2μm-1μm 以下.

以輝達的最新的晶片為例, 其 Die 的尺寸是 50mmx54mm, 一片 12" 的晶圓可以放 14 顆這樣的 Die; 但有消息稱, 正在打樣的下一代產品中的 Die 的尺寸將達到 120mmx150mm, 那麽單片 12" 的晶圓就只能容納 1 顆Die. 這麽大的晶片, 要保障其整體良率是非常困難的, 只要在個別點上出現問題, 整片晶圓報廢, 相比之下, 面板級封裝的產能和成本優勢都非常明顯.

FOPLP 和 CoPoS 均採用大型面板基板進行封裝, 但它們在架構和應用方面存在顯著差異, 尤其是在中介層的使用方面. FOPLP 是一種無需中介層的封裝方法, 晶片直接重新分佈在面板基板上, 並透過 RDL 進行互連. CoPoS 採用了中介層, 從而實現了更高的訊號完整性和穩定的功率傳輸, 中介層的存在使 CoPoS 更適合需要大面積封裝和高速資料傳輸的高階 AI 和 HPC 系統.

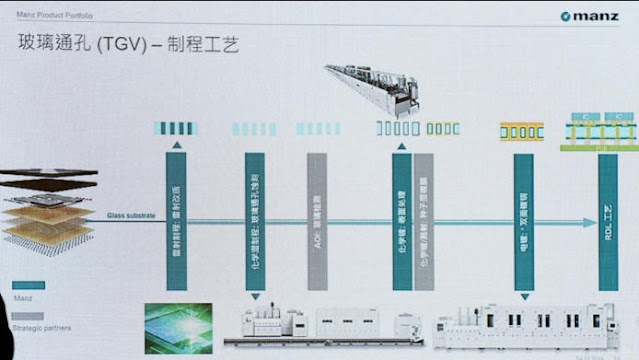

FOPLP 技術已經開始量產, 當然目前量產的主要是功率器件, 傳感器和射頻等小面積晶片. 在大面積晶片上, 還處於探索階段. CoPoS 領域的另一個熱詞就是 TGV; 即穿過玻璃基板的垂直電氣互連. TGV 以高品質硼矽玻璃, 石英玻璃為基材, 通過種子層濺射, 電鍍填充, CMP, RDL 再布線, bump 工藝引出實現 3D 互聯, 因此被視為下一代 3D 集成的關鍵技術.

與傳統的有機基板相比, 玻璃具有獨特的性能, 例如玻璃基板具備超低平坦度, 更高散熱性和更佳的機械穩定性, 有望進一步提高基板互連密度. 同時, TGV 為具有挑戰性且昂貴的矽技術提供了一種成本更低, 損耗更低的替代方案. 所以, 雖然當前 TGV 主要是用作玻璃芯, 但當工藝更加成熟時, 或可用 TGV 替代中介層.

台積電已經投資建設 CoPoS 310mm² 試產線, ASE 幾乎同期發布採用 300 mm² 面板的 2.5D 封裝技術 (FOCoS-Bridge). CoPoS 提供更大規模的先進封裝 I/O 與 HBM 堆疊數, 極大程度緩解先進封裝產能供不應求與初步流片, 晶片制造的高成本. CoPoS 的面板級面積+HBM 堆疊組合能帶來比現行 CoWoS 更大的帶寬/容量擴增.

CoPoS 的面板可利用率高, 面積約等於圓片 3-5 倍, 疊加潛在產能提升 ×2-×3, 單位面積成本降低約 20-30%, 半導體設備鏈可能需重新適配 (主要集中於大型雷射分割, 直接成像光刻以及真空貼片機). 從 12" 晶圓級設備跨到 PLP相關原材料與設備是一輪全新的超大規模 CAPEX 周期, 半導體設備巨頭們 (如 Disco, Ulvac, Screen HD, Canon) 有望獲得增量訂單.

面板級封裝是半導體行業近年來重點發展的先進封裝技術, FOPLP 與 CoPoS 均屬於面板級晶片封裝, 雖均採用大尺寸面板, 但設計理念和適用領域不同. FOPLP 主要面向中端市場, 而 CoPoS 則服務於高性能計算領域. 台灣半導體供應鏈已將面板級封裝視為下一代先進封裝技術的關鍵戰場. 群創, 日月光也在 FOPLP 上積極布局, 而台積電則將 CoPoS 作為重要戰略方向.

FOPLP 和 CoPoS 均採用大型面板基板進行封裝, 但它們在架構和應用方面存在顯著差異, 尤其是在中介層的使用方面. FOPLP 是一種無需中介層的封裝方法, 晶片直接重新分佈在面板基板上, 並透過 RDL 進行互連. CoPoS 採用了中介層, 從而實現了更高的訊號完整性和穩定的功率傳輸, 中介層的存在使 CoPoS 更適合需要大面積封裝和高速資料傳輸的高階 AI 和 HPC 系統.

FOPLP 技術已經開始量產, 當然目前量產的主要是功率器件, 傳感器和射頻等小面積晶片. 在大面積晶片上, 還處於探索階段. CoPoS 領域的另一個熱詞就是 TGV; 即穿過玻璃基板的垂直電氣互連. TGV 以高品質硼矽玻璃, 石英玻璃為基材, 通過種子層濺射, 電鍍填充, CMP, RDL 再布線, bump 工藝引出實現 3D 互聯, 因此被視為下一代 3D 集成的關鍵技術.

與傳統的有機基板相比, 玻璃具有獨特的性能, 例如玻璃基板具備超低平坦度, 更高散熱性和更佳的機械穩定性, 有望進一步提高基板互連密度. 同時, TGV 為具有挑戰性且昂貴的矽技術提供了一種成本更低, 損耗更低的替代方案. 所以, 雖然當前 TGV 主要是用作玻璃芯, 但當工藝更加成熟時, 或可用 TGV 替代中介層.

台積電已經投資建設 CoPoS 310mm² 試產線, ASE 幾乎同期發布採用 300 mm² 面板的 2.5D 封裝技術 (FOCoS-Bridge). CoPoS 提供更大規模的先進封裝 I/O 與 HBM 堆疊數, 極大程度緩解先進封裝產能供不應求與初步流片, 晶片制造的高成本. CoPoS 的面板級面積+HBM 堆疊組合能帶來比現行 CoWoS 更大的帶寬/容量擴增.

CoPoS 的面板可利用率高, 面積約等於圓片 3-5 倍, 疊加潛在產能提升 ×2-×3, 單位面積成本降低約 20-30%, 半導體設備鏈可能需重新適配 (主要集中於大型雷射分割, 直接成像光刻以及真空貼片機). 從 12" 晶圓級設備跨到 PLP相關原材料與設備是一輪全新的超大規模 CAPEX 周期, 半導體設備巨頭們 (如 Disco, Ulvac, Screen HD, Canon) 有望獲得增量訂單.

面板級封裝是半導體行業近年來重點發展的先進封裝技術, FOPLP 與 CoPoS 均屬於面板級晶片封裝, 雖均採用大尺寸面板, 但設計理念和適用領域不同. FOPLP 主要面向中端市場, 而 CoPoS 則服務於高性能計算領域. 台灣半導體供應鏈已將面板級封裝視為下一代先進封裝技術的關鍵戰場. 群創, 日月光也在 FOPLP 上積極布局, 而台積電則將 CoPoS 作為重要戰略方向.

台積電CoPoS傳量產廠將落腳嘉義AP7

回覆刪除https://www.moneydj.com/kmdj/news/newsviewer.aspx?a=b0c84602-eb91-409c-8b33-e254a7865925

台積電「CoPoS」封裝技術聚焦 AI 與高效能運算設計,預計2028年底量產

回覆刪除https://www.techbang.com/posts/123718-tsmc-copos-packaging-for-ai-hpc-2028

台积电CoPoS封装技术聚焦AI与高性能计算:明年首设实验线

回覆刪除https://finance.sina.com.cn/tech/discovery/2025-06-11/doc-inezskcq8157861.shtml

台积电:推进美国2nm晶圆厂建设,全力攻克CoPoS封装

回覆刪除https://www.eet-china.com/mp/a412698.html

从CoWoS到CoPoS:台积电掀起一场席卷芯片产业链的“先进封装变革”

回覆刪除https://finance.sina.com.cn/stock/hkstock/ggscyd/2025-07-03/doc-infefhcc3230446.shtml

FOPLP Heats Up: ASE, Powertech Expand; TSMC Reportedly Preps 2026 CoPoS Pilot Line

回覆刪除https://www.trendforce.com/news/2025/06/18/news-foplp-heats-up-ase-powertech-expand-tsmc-reportedly-preps-2026-copos-pilot-line/

台积电CoWoS的接班人:CoPoS

回覆刪除https://news.qq.com/rain/a/20250703A083AE00